|

ГЛАВНАЯ

> Вернуться к содержанию

Кибернетика и программирование

Правильная ссылка на статью:

Сибиряков М.А., Сухих А.В., Иванов К.В., Кошпаев А.А.

Построение вычислительного кластера на основе коммуникационной среды PCI Express

// Кибернетика и программирование.

2015. № 5.

С. 173-180.

DOI: 10.7256/2306-4196.2015.5.17035 URL: https://nbpublish.com/library_read_article.php?id=17035

Построение вычислительного кластера на основе коммуникационной среды PCI Express

Сибиряков Максим Андреевич

кандидат технических наук

руководитель, группа компьютерного обеспечения ГТРК Марий Эл

424033, Россия, Республика Марий Эл, г. Йошкар-Ола, ул. Эшкинина, 2

Sibiryakov Maksim Andreevich

PhD in Technical Science

The head of the computer support group of GTRK Mari El

424033, Russia, respublika Marii El, g. Ioshkar-Ola, ul. Eshkinina, 2

|

maxover777@bk.ru

|

|

|

Другие публикации этого автора

|

|

Сухих Андрей Владимирович

аспирант, кафедра Информационно-вычислительных систем, Поволжский государственный технологический университет

424000, Россия, Марий Эл область, г. Йошкар-Ола, ул. Пл. Ленина, 3

Sukhikh Andrei Vladimirovich

graduate student, Volga State University of Technology

424000, Russia, Marii El, g. Ioshkar-Ola, pl. Lenina, 3

|

maddas666@ya.ru

|

|

|

Иванов Константин Владимирович

аспирант, кафедра Информационно-вычислительных систем, Поволжский государственный технологический университет

424000, Россия, Марий Эл область, г. Йошкар-Ола, ул. Пл. Ленина, 3

Ivanov Konstantin Vladimirovich

graduate student, Volga State University of Technology

424000, Russia, Marii El, g. Ioshkar-Ola, pl. Lenina, 3

|

ikv1992@yandex.ru

|

|

|

|

Кошпаев Андрей Алексеевич

аспирант, кафедра Информационно-вычислительных систем, Поволжский государственный технологический университет

424000, Россия, Марий Эл область, г. Йошкар-Ола, ул. Пл. Ленина, 3

Koshpaev Andrei Alekseevich

graduate student, Volga State University of Technology

424000, Russia, Marii El, g. Ioshkar-Ola, pl. Lenina, 3

|

koshpaev1991@yandex.ru

|

|

|

|

DOI: 10.7256/2306-4196.2015.5.17035

Дата направления статьи в редакцию:

20-11-2015

Дата публикации:

27-11-2015

Аннотация:

В данной статье рассматривается вопрос реализации производительного и надежного кластера с низкими стоимостными характеристиками. В качестве решения предлагается построение кластерной системы на базе протокола ввода/вывода данных PCI Express. Основной целью является поиск способов увеличения производительности кластерной системы и ее коммутационной среды. В качестве предмета исследования выступают алгоритмы передачи и обработки данных в коммутаторе, алгоритмы поиска и вытеснения данных в системе хранения данных, схемы арбитража портов коммутатора. Методология исследования - структурный системный анализ предметной области в части коммутационных структур, построения кэш-памяти систем хранения данных, способов построения кластерных систем. В статье предлагаются следующие структурные и алгоритмические решения: модифицированный алгоритм трансляции адресов внешнего коммутатора PCI Express; усовершенствованный метод и алгоритм поиска и обработки данных в кэш-памяти системы хранения данных на основе уникального хеширования; формализация всех ступеней алгоритмов арбитража портов и виртуальных каналов коммутатора.

Ключевые слова:

кластеры, коммуникационная сеть, протокол PCI Express, системы хранения данных, кэш-память, коммутатор, арбитраж портов, трансляция адресов, хеширование, ПЛИС

УДК: 004.75

Abstract: The article discusses the implementation of a productive and reliable cluster with low cost. As a solution, the authors recommend building a cluster system based on the PCI Express data input / output protocol. The main goal is to find ways to increase the productivity of the cluster system and its circuit protection. The subjects of the study are the algorithms for data transfer and processing on the switch, algorithms for search and displacement data in storage system, switch ports arbitration scheme. The research methodology includes structured systems analysis in the domain of the connection structures, the construction of cache storage, methods of constructing cluster systems. The authors propose the following structural and algorithmic solutions: a modified algorithm for address translation of the external PCI Express Switch; an improved method and algorithm for data searching and processing in the cache data storage systems based on a unique hash; formalization of all stages of arbitration algorithms for ports and virtual switch channels.

Keywords: clusters, communications network, PCI Express protocol, data storage, a cache memory, switch, Port arbitration, address translation, hashing, FPGA

Введение Кластерные системы представляют собой совокупность вычислительных узлов, объединенных высокоскоростной сетью [1, 2]. Они предназначены для решения сложных вычислительных задач. В настоящее время применение кластерных систем получило широкое распространение. Они используются как в суперкомпьютерных центрах, так и на предприятиях и в организациях. С помощью кластера можно решить множество трудоёмких задач в различных отраслях науки, бизнеса и промышленности:

● в технологических процессах, в банковском деле, фармацевтике, энергетике, телекоме;

● при моделировании нефтяных и газовых месторождений;

● при проведении фундаментальных исследований в области физики, астрономии, молекулярной биологии, генетике и многих других.

Использование кластеров в бизнесе достаточно дорогостоящий проект, поэтому актуальной задачей является создание кластерных систем, обеспечивающих высокую производительность и надежность при низкой стоимости. Одним из таких решений является кластерная система на основе протокола PCI Express, обеспечивающая хорошую производительность и надежность на уровне, сравнимом с дорогостоящими аналогами. Структура кластерной системы на основе PCI Express Структура кластерной системы на основе PCIExpress

В общем виде кластерная система включает в себя: вычислительные узлы, выполняющие обработку данных; систему хранения данных (хранилище данных) и коммутационную сеть, в основе которой лежит коммутатор (рис. 1).

Рис. 1. Базовая структура кластерной системы

Коммутационная сеть значительно влияет на основные характеристики скорости передачи данных и производительности кластерной системы [3]. Поэтому важным моментом является повышение эффективности ее работы, т.е. повышение пропускной способности сети без снижения QoS.

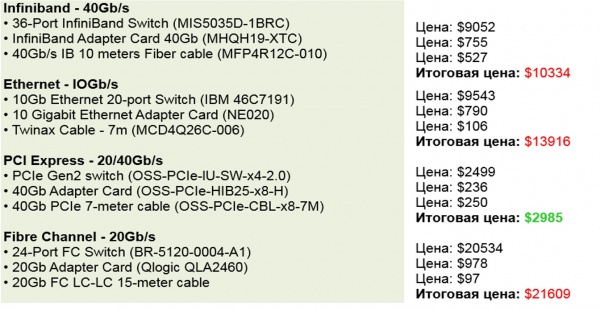

Обычно коммутационная сеть строится на базе высокопроизводительных протоколов передачи данных, таких как Ethernet, Fibre Channel, InfiniBand и PCI Express. Использование сетевой инфраструктуры на базе протокола PCI Express имеет недостаток в сравнении с аналогами - ограничение по длине кабельной системы, соответственно и по дальности размещения вычислительных узлов и хранилищ данных. Однако, стоимость кластерной системы на базе PCI Express значительно ниже. На рис. 2 представлено сравнение стоимостных характеристик оборудования для разных коммуникационных сред. Таким образом, низкая стоимость позволит строить небольшие кластерные системы для среднего и малого сегмента: небольших бизнес-предприятий и организаций, для которых характерно небольшое территориальное удаление узлов.

Рис. 2. Сравнение стоимостных характеристик сетевой инфраструктуры на базе основных протоколов передачи данных

Производительность кластера на базе PCI Express можно повысить путем улучшения алгоритмов обработки, пересылки и доступа к данным, хранимым в системах хранения данных. Авторами статьи для повышения эффективности кластерной системы на основе протокола PCI Express предлагаются решения ряда задач:

1) разработка модифицированного алгоритма трансляции адресов в непрозрачных портах коммутатора PCI Express и его реализация на ПЛИС;

2) реализация оптимальной схемы арбитража портов коммутатора;

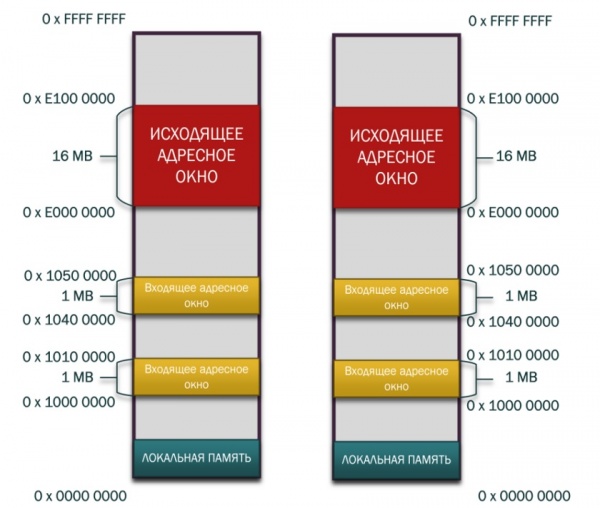

3) модификация алгоритмов обработки данных в кэш-памяти системы хранения данных. Алгоритм трансляции адресов в портах коммутатора PCI Express В рамках первой задачи разработан алгоритм трансляции адресов во входных портах коммутатора PCI Express, который позволяет транслировать адреса в непрозрачных портах с большей эффективностью, чем существующие алгоритмы прямой трансляции или LT-алгоритмы. Алгоритм позволяет сопоставить адреса двух вычислительных узлов кластерной системы, принадлежащих к разным адресным доменам, применяя специальный механизм трансляции адресов от исходящего адресного узла отправителя к входящему адресному узлу (рис. 3) [4-8].

Рис. 3. Распределение адресного пространства в узлах кластерной системы.

Использование нового алгоритма предполагает снижение времени прохождения пакетов через коммутирующее устройство. Это позволит повысить эффективную скорость передачи данных. Кроме того, в данном случае не требуется модификация самого протокола. Алгоритм базируется на поиске транслированного адреса по первым двум байтам адреса получателя, указанного в пакете уровня транзакций. Незначительной модификации требует лишь формат таблицы трансляции адресов. Поскольку транслированный и исходный адреса однозначно сопоставляются друг другу, то целесообразней не проводить поиск в таблице трансляции по искусственно введенному полю «Index», а определять соответствующий транслированный адрес по старшим битам исходного адреса. Аппаратная реализация самого устройства коммутатора не изменится, поскольку в новом алгоритме поиска будут задействованы те же самые наборы регистров.

Алгоритм поиска транслированного адреса в таблице трансляции хорошо распараллеливается. В данном случае целесообразнее использовать параллелизм независимых ветвей. Распараллеленный алгоритм несложно запрограммировать в ПЛИС. Исследование схемы арбитража входных потоков На этапе решения второй задачи реализации оптимальной схемы арбитража портов коммутатора исследованы алгоритмы арбитража и виртуальных каналов коммутатора PCI Express, описанных в спецификации протокола PCI Express 3.0.

Система арбитража PCI Express является двухступенчатой (рис. 4), при этом первая ступень решает задачу обеспечения доступа потокам пакетов с разных входных портов, а вторая ступень решает задачу распределения потоков с учетом приоритетов. Такая организация является избыточной, что подчеркивается самими авторами спецификации [6], поскольку на каждый выходной порт требуется число аппаратных очередей, соответствующее числу входных портов, а затем потоки группируются в 8 выходных очередей, что соответствует числу виртуальных каналов. Но такое большое число является оправданным, поскольку позволяет равномерно распределять потоки с разных входных портов с учетом принадлежности разным виртуальным каналам.

Рис. 4. Схема арбитража портов коммутатора

В результате исследований был разработан и исследован алгоритм работы всех ступеней арбитража. Применение более эффективной схемы арбитража портов позволит ускорить обработку пакетов передачи данных в коммутаторе [9]. За счет этого повысится скорость передачи данных через коммутатор.

На обеих ступенях арбитража в коммутаторе PCI Express происходит ранжирование трафика по приоритетам с поддержкой циклической и взвешенной циклической схем приоритетов. Арбитр виртуальных каналов, кроме того, дает возможность использовать схему со строгими приоритетами одновременно с упомянутыми схемами. При этом виртуальные каналы делятся на две группы, размеры которых зависят от настройки, устанавливающей границу между группами.

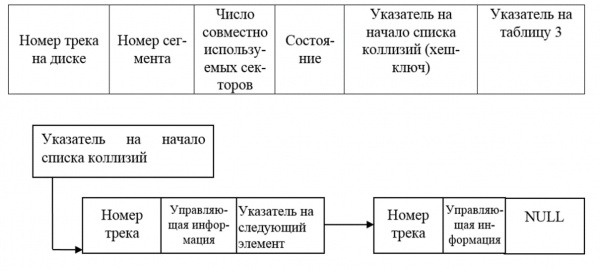

Для исследований алгоритма на языке программирования C++ была написана имитационная модель арбитра коммутатора PCI Express [10-12]. В результате моделирования получены зависимости средней длины очереди от интенсивности входного потока пакетов для разных ступеней арбитража, что позволяет проследить динамику поведения арбитра в зависимости от его нагрузки и распределения входных пакетов по виртуальным каналам. Алгоритмы работы кэш-памяти системы хранения данных В рамках третьей задачи были исследованы существующие методы управления кэш-памятью систем хранения данных; детально проанализированы алгоритмы чтения, записи и вытеснения данных, а также структуры данных [13 - 15].На основании произведенных исследований разработан метод поиска данных в кэш-памяти системы хранения данных на основе уникального хеширования. За счет применения новой структуры данных – индексной хеш-таблицы адресов дискового кэша (рис. 5) увеличивается скорость выполнения операции поиска блоков данных.

Рис. 5. Структура данных на основе уникального хеширования

Это приводит к уменьшению времени выполнения алгоритмов обработки данных в кэш-памяти, что позволит увеличить скорость доступа к хранимым данным и производительность кластерной системы в целом. Вдальнейшем планируется распараллеливание алгоритма поиска данных в кэш-памяти СХД и его аппаратная реализация на ПЛИС.

Библиография

1. Лацис, А.О. Как построить и использовать суперкомпьютер / А. О. Лацис.-М.:Бестселлер, 2003. – 240 с.

2. Корнеев, В. В. Вычислительные системы / В.В. Корнеев – М.: Ге-лиос АРВ, 2004. – 438с.

3. Берлин, А.Н. Коммутация в системах и сетях связи / А.Н. Берлин – М.: Эко-Тренд, 2006. – 341с.

4. Петров, С.Г. Шины PCI, PCI Express. Архитектура, дизайн, прин-ципы функционирования / С.Г. Петров – СПб.: БХВ – Петербург, 2006. – 405с.

5. Сухих, А.В. Структура параллельной вычислительной системы с распределенной внешней памятью / А.В. Сухих, Н.С. Васяева // «Инфор-мационные технологии в профессиональной деятельности и научной рабо-те»: всерос. научн.-практич. конф. – МарГТУ, Йошкар-Ола, 2012, том I, с.172-177.

6. PCI Express Base Specification. Revision 3.0 Режим доступа: https://members.pcisig.com/wg/PCI-SIG/document/download/8269

7. Regula, J. Using Non-transparent Bridging in PCI Express Systems / J. Regula – PLX Technology, Inc., 2004. – 31c.

8. Increase of productivity of the PCI Express switch for cluster systems/ Vasjaeva N.S., Ivanov K.V., Suhih A.V.// В мире научных открытий.-Крас-ноярск: Научно-инновационный центр, 2014. № 10(58) (Естественные и технические науки). –c. 248-262.

9. Бронштейн, И. О. Модели приоритетного обслуживания в инфор-мационно-вычислительных системах / И.О. Бронштейн, И.М. Духовный – М.: Наука, 1976. – 220с.

10. Иванов К.В., Кошпаев А.А., Васяева Н.С. Программная модель системы арбитража коммутатора PCI Express // Кибернетика и програм-мирование. — 2014.-№ 4.-С.66-75. DOI: 10.7256/2306-4196.2014.4.12758. URL: http://e-notabene.ru/kp/article_12758.html

11. Васяева, Н.С., Формальное представление алгоритма арбитража виртуальных каналов на шине PCI Express/ Н.С. Васяева Н.С., К.В. Ива-нов – Сборник материалов Всероссийской научно-практической конфе-ренции с международным участием «Информационные технологии в про-фессиональной деятельности и научной работе».-Йошкар-Ола: ПГТУ, 2014. – с. 223-229.

12. Васяева, Н.С. Моделирование и оптимизация системы арбитража для протокола PCI Express/ Н.С. Васяева Н.С., К.В. Иванов – Труды международной научной конференции «Параллельные вычислительные технологии (ПаВТ’2015)» (г. Екатеринбург, 31 марта – 2 апреля 2015 г.).-Челябинск: Издательский центр ЮУрГУ, 2015. с. 503 с.

13. Сибиряков, М.А. Применение хеширования для построения ин-дексных таблиц кэша в системах хранения данных / М.А. Сибиряков // Ма-териалы международной научно-практической конференции «Информа-ционные технологии. Проблемы и решения». – Уфа, 2015, том II, с.205-209.

14. Васяева, Е.С. Разработка структуры индексных таблиц кэш-памяти системы хранения данных/ Е.С. Васяева Е.С., А.А. Кошпаев– Сборник материалов Всероссийской научно-практической конференции с международным участием «Информационные технологии в профессио-нальной деятельности и научной работе».-Йошкар-Ола: ПГТУ, 2014. – с. 214-222.

15. Sibiryakov, M.A. Analysis and comparison of cache memory control methods/ E.S. Vasyaeva, M.A. Sibiryakov, A.A. Koshpaev // В мире научных открытий.-Красноярск: Научно-инновационный центр, 2014. № 10(58) (Естественные и технические науки). –c. 263-280.

References

1. Latsis, A.O. Kak postroit' i ispol'zovat' superkomp'yuter / A. O. Latsis.-M.:Bestseller, 2003. – 240 s.

2. Korneev, V. V. Vychislitel'nye sistemy / V.V. Korneev – M.: Ge-lios ARV, 2004. – 438s.

3. Berlin, A.N. Kommutatsiya v sistemakh i setyakh svyazi / A.N. Berlin – M.: Eko-Trend, 2006. – 341s.

4. Petrov, S.G. Shiny PCI, PCI Express. Arkhitektura, dizain, prin-tsipy funktsionirovaniya / S.G. Petrov – SPb.: BKhV – Peterburg, 2006. – 405s.

5. Sukhikh, A.V. Struktura parallel'noi vychislitel'noi sistemy s raspredelennoi vneshnei pamyat'yu / A.V. Sukhikh, N.S. Vasyaeva // «Infor-matsionnye tekhnologii v professional'noi deyatel'nosti i nauchnoi rabo-te»: vseros. nauchn.-praktich. konf. – MarGTU, Ioshkar-Ola, 2012, tom I, s.172-177.

6. PCI Express Base Specification. Revision 3.0 Rezhim dostupa: https://members.pcisig.com/wg/PCI-SIG/document/download/8269

7. Regula, J. Using Non-transparent Bridging in PCI Express Systems / J. Regula – PLX Technology, Inc., 2004. – 31c.

8. Increase of productivity of the PCI Express switch for cluster systems/ Vasjaeva N.S., Ivanov K.V., Suhih A.V.// V mire nauchnykh otkrytii.-Kras-noyarsk: Nauchno-innovatsionnyi tsentr, 2014. № 10(58) (Estestvennye i tekhnicheskie nauki). –c. 248-262.

9. Bronshtein, I. O. Modeli prioritetnogo obsluzhivaniya v infor-matsionno-vychislitel'nykh sistemakh / I.O. Bronshtein, I.M. Dukhovnyi – M.: Nauka, 1976. – 220s.

10. Ivanov K.V., Koshpaev A.A., Vasyaeva N.S. Programmnaya model' sistemy arbitrazha kommutatora PCI Express // Kibernetika i program-mirovanie. — 2014.-№ 4.-S.66-75. DOI: 10.7256/2306-4196.2014.4.12758. URL: http://e-notabene.ru/kp/article_12758.html

11. Vasyaeva, N.S., Formal'noe predstavlenie algoritma arbitrazha virtual'nykh kanalov na shine PCI Express/ N.S. Vasyaeva N.S., K.V. Iva-nov – Sbornik materialov Vserossiiskoi nauchno-prakticheskoi konfe-rentsii s mezhdunarodnym uchastiem «Informatsionnye tekhnologii v pro-fessional'noi deyatel'nosti i nauchnoi rabote».-Ioshkar-Ola: PGTU, 2014. – s. 223-229.

12. Vasyaeva, N.S. Modelirovanie i optimizatsiya sistemy arbitrazha dlya protokola PCI Express/ N.S. Vasyaeva N.S., K.V. Ivanov – Trudy mezhdunarodnoi nauchnoi konferentsii «Parallel'nye vychislitel'nye tekhnologii (PaVT’2015)» (g. Ekaterinburg, 31 marta – 2 aprelya 2015 g.).-Chelyabinsk: Izdatel'skii tsentr YuUrGU, 2015. s. 503 s.

13. Sibiryakov, M.A. Primenenie kheshirovaniya dlya postroeniya in-deksnykh tablits kesha v sistemakh khraneniya dannykh / M.A. Sibiryakov // Ma-terialy mezhdunarodnoi nauchno-prakticheskoi konferentsii «Informa-tsionnye tekhnologii. Problemy i resheniya». – Ufa, 2015, tom II, s.205-209.

14. Vasyaeva, E.S. Razrabotka struktury indeksnykh tablits kesh-pamyati sistemy khraneniya dannykh/ E.S. Vasyaeva E.S., A.A. Koshpaev– Sbornik materialov Vserossiiskoi nauchno-prakticheskoi konferentsii s mezhdunarodnym uchastiem «Informatsionnye tekhnologii v professio-nal'noi deyatel'nosti i nauchnoi rabote».-Ioshkar-Ola: PGTU, 2014. – s. 214-222.

15. Sibiryakov, M.A. Analysis and comparison of cache memory control methods/ E.S. Vasyaeva, M.A. Sibiryakov, A.A. Koshpaev // V mire nauchnykh otkrytii.-Krasnoyarsk: Nauchno-innovatsionnyi tsentr, 2014. № 10(58) (Estestvennye i tekhnicheskie nauki). –c. 263-280.

Ссылка на эту статью

Просто выделите и скопируйте ссылку на эту статью в буфер обмена. Вы можете также

попробовать найти похожие

статьи

|

|